ؤگل»ƒ giأ؛p anh/chل»‹ quyل؛؟t ؤ‘ل»‹nh cأ³ ؤ‘ل»چc tiل؛؟p hay khأ´ng, tأ´i xin phأ©p cung cل؛¥p cأ،c thأ´ng tin liأھn quan ؤ‘ل؛؟n bأ i post nأ y nhئ° sau:

- Chل»§ ؤ‘ل»پ: Electronics (ؤ‘iل»‡n tل»)

- Tأnh thل»i sل»±: Thأ،ng 04/2024

- Thل»i gian ؤ‘ل»چc: 25 phأ؛t, kل»ƒ cل؛£ thل»i gian uل»‘ng cأ phأھ (uل»‘ng cأ phأھ xong lأ ؤ‘ل»چc xong)

ً’پˆ

â’¶. ؤگل»پ dل؛«n

Thل؛¥y bأ،o chأ gل؛§n ؤ‘أ¢y nأ³i nhiل»پu vل»پ chip ؤ‘iل»‡n tل» nأھn hأ´m nay xin phأ©p anh/chل»‹ trأھn diل»…n ؤ‘أ n nhأ n ؤ‘أ m vل»پ viل»‡c sل؛£n xuل؛¥t ra semiconductor chips. Hoل؛·c tأھn gل»چi khأ،c lأ quy trأ¬nh sل؛£n xuل؛¥t ra IC (Integrated Circuit), sل؛£n xuل؛¥t chip.

Cأ،i mأ tأ´i (vأ cأ³ thل»ƒ mل»™t sل»‘ anh/chل»‹ khأ،c nل»¯a) tأ² mأ² lأ ngئ°ل»i ta sل؛£n xuل؛¥t ra semiconductor chips nhئ° thل؛؟ nأ o. ؤگل»ƒ cho dل»… hأ¬nh dung: tأ´i tin lأ trأھn diل»…n ؤ‘أ n nأ y cأ³ nhiل»پu anh/chل»‹ ؤ‘أ£ trل؛£i nghiل»‡m viل»‡c thiل؛؟t kل؛؟ mل؛،ch ؤ‘iل»‡n tل», tiل؛؟p ؤ‘أ³ lأ m mل؛،ch in, rل»“i ؤ‘ئ°a mل؛،ch in vل»«a lأ m ؤ‘أ³ vأ o ل»©ng dل»¥ng trong thل»±c tل؛؟. Viل»‡c sل؛£n xuل؛¥t chip cأ³ thل»ƒ vأ nhئ° viل»‡c lأ m mل؛،ch in nhئ°ng vل»›i mل»©c ؤ‘ل»™ tinh vi hئ،n. (ًںکٹ)

Sau phل؛§n nل»™i dung chأnh nguyأھn lأ½ sل؛£n xuل؛¥t chip, bأ i post nأ y cأ³ bأ n mل»™t vأ i dأ²ng vل»پ thل»‹ phل؛§n sل؛£n xuل؛¥t chip trأھn thل؛؟ giل»›i vأ phأ،c hل»چa mل»™t bل»©c tranh sئ، lئ°ل»£c vل»پ phأ¢n bل»‘ ؤ‘ل»‹a lأ½ cأ،c cأ´ng ty chuyأھn vل»پ lؤ©nh vل»±c nأ y.

ً’پˆ

â’·. Semiconductor

Xin nأ³i qua mل»™t chأ؛t vل»پ semiconductor (chل؛¥t bأ،n dل؛«n) vأ transistor (bأ³ng bأ،n dل؛«n). Vأ¬ nأ³i cho cأ¹ng thأ¬ ؤ‘أ¢y lأ khل»ںi thل»§y cل»§a thل؛؟ giل»›i hiل»‡n ؤ‘ل؛،i: tل»« chل؛¥t bأ،n dل؛«n → bأ³ng bأ،n dل؛«n → vi mل؛،ch → IC → mأ،y tأnh → mل؛،ng Internet → trأ tuل»‡ nhأ¢n tل؛،o → …

-

Chل؛¥t bأ،n dل؛«n lأ loل؛،i vل؛t liل»‡u khأ´ng hل؛³n dل؛«n ؤ‘iل»‡n (nhئ° kim loل؛،i), mأ cإ©ng khأ´ng hل؛³n lأ ؤ‘iل»‡n trل»ں (nhئ° thل»§y tinh). Nأ³ nل؛±m giل»¯a dل؛«n ؤ‘iل»‡n vأ ؤ‘iل»‡n trل»ں. Vل؛t liل»‡u bأ،n dل؛«n ؤ‘ئ°ل»£c sل» dل»¥ng phل»• biل؛؟n nhل؛¥t trong bأ³ng bأ،n dل؛«n lأ silicon, mل؛·c dأ¹ cأ،c vل؛t liل»‡u khأ،c nhئ° germanium cإ©ng ؤ‘ئ°ل»£c sل» dل»¥ng trong mل»™t sل»‘ trئ°ل»ng hل»£p. Vأ¬ vل؛y, trong phل؛§n tiل؛؟p theo, tأ´i xin chل»‰ ؤ‘ل»پ cل؛p ؤ‘ل؛؟n silicon.

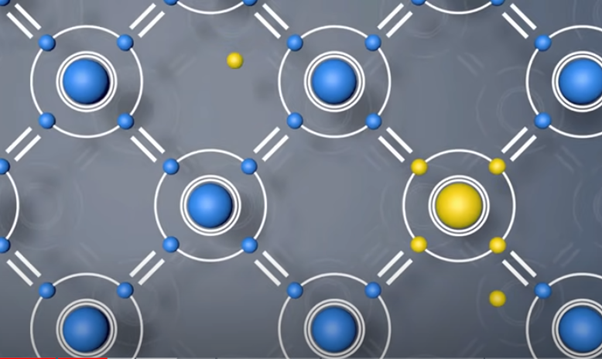

Silicon (Si) ؤ‘ئ°ل»£c tل؛،o thأ nh tل»« cأ،c nguyأھn tل» riأھng lل؛» liأھn kل؛؟t vل»›i nhau theo cل؛¥u trأ؛c ؤ‘ل»پu ؤ‘ل؛·n, tuل؛§n hoأ n tل؛،o thأ nh mل؛،ng lئ°ل»›i cأ،c nguyأھn tل» trong ؤ‘أ³ mل»—i nguyأھn tل» ؤ‘ئ°ل»£c bao quanh bل»ںi cأ،c electron. Mل»™t nguyأھn tل» riأھng lل؛» bao gل»“m mل»™t hل؛،t nhأ¢n ؤ‘ئ°ل»£c tل؛،o thأ nh tل»« lأµi proton (hل؛،t tأch ؤ‘iل»‡n dئ°ئ،ng) vأ neutron (hل؛،t khأ´ng tأch ؤ‘iل»‡n) ؤ‘ئ°ل»£c bao quanh bل»ںi cأ،c electron (tأch ؤ‘iل»‡n أ¢m). Sل»‘ lئ°ل»£ng electron vأ proton bل؛±ng nhau, sao cho nguyأھn tل» trung hأ²a vل»پ ؤ‘iل»‡n. Cأ،c electron bao quanh mل»—i nguyأھn tل» trong chل؛¥t bأ،n dل؛«n lأ mل»™t phل؛§n cل»§a liأھn kل؛؟t cل»™ng hأ³a trل»‹. Liأھn kل؛؟t cل»™ng hأ³a trل»‹ bao gل»“m hai nguyأھn tل» “chia sل؛»” mل»™t cل؛·p electron. Mل»—i nguyأھn tل» tل؛،o thأ nh 4 liأھn kل؛؟t cل»™ng hأ³a trل»‹ vل»›i 4 nguyأھn tل» xung quanh. Do ؤ‘أ³, giل»¯a mل»—i nguyأھn tل» vأ 4 nguyأھn tل» xung quanh nأ³ cأ³ 8 electron ؤ‘ئ°ل»£c chia sل؛». Cل؛¥u trأ؛c cل»§a chل؛¥t bأ،n dل؛«n ؤ‘ئ°ل»£c thل»ƒ hiل»‡n trong hأ¬nh dئ°ل»›i ؤ‘أ¢y.

Hأ¬nh 1: Mل؛،ng lئ°ل»›i tinh thل»ƒ cل»§a silicon

-

Pha tل؛،p chل؛¥t (Doping)

Nل؛؟u ؤ‘ل»ƒ y nguyأھn mل؛،ng lئ°ل»›i tinh thل»ƒ cل»§a silicon thأ¬ chل؛³ng cأ³ chuyل»‡n gأ¬ xل؛£y ra cل؛£ vأ¬ mل؛،ng tinh thل»ƒ nأ y ل»ں trل؛،ng thأ،i cأ¢n bل؛±ng. Tuy nhiأھn, cأ³ thل»ƒ lأ m thay ؤ‘ل»•i sل»± cأ¢n bل؛±ng cل»§a mل؛،ng tinh thل»ƒ silicon bل؛±ng cأ،ch “pha tل؛،p” nأ³ vل»›i cأ،c nguyأھn tل» khأ،c. Cأ،ch lأ m nأ y cأ³ tأھn gل»چi lأ doping. Cأ³ 2 cأ،ch pha tل؛،p chل؛¥t vأ o khل»‘i silicon tinh khiل؛؟t.

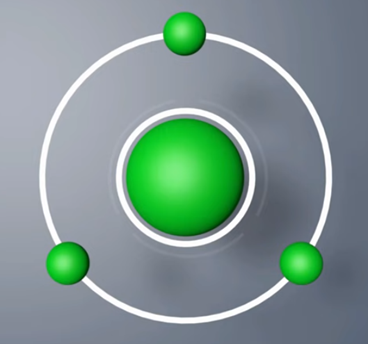

â‘ Cأ،ch thل»© nhل؛¥t: ngئ°ل»i ta lل؛¥y cأ،c nguyأھn tل»‘ trong nhأ³m V cل»§a bل؛£ng tuل؛§n hoأ n ؤ‘ل»ƒ pha tل؛،p. Xem cل؛¥u trأ؛c tinh thل»ƒ cل»§a nhأ³m nأ y chأ؛ng ta thل؛¥y bao quanh hل؛،t nhأ¢n cأ³ 5 electron (xem Hأ¬nh 2 dئ°ل»›i ؤ‘أ¢y).

Hأ¬nh 2: Cل؛¥u trأ؛c tinh thل»ƒ cل»§a nguyأھn tل»‘ dل؛£i hأ³a trل»‹ 5 (Antimony, Phosphorus, Arsenic)

-

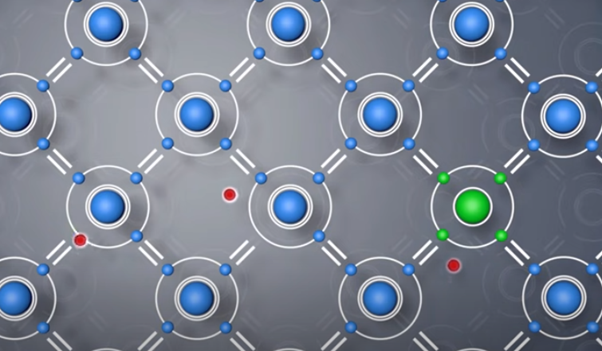

Sau khi “nhأ©t” nguyأھn tل»‘ cأ³ 5 electron bao quanh vأ o thل؛؟ chل»— cho mل»™t tinh thل»ƒ silicon ؤ‘ang cأ¢n bل؛±ng vل»›i 4 electron bao quanh thأ¬ mل»™t electron “thل»«a” bل»‹ ؤ‘ل؛©y ra khل»ڈi mل؛،ng lئ°ل»›i tinh thل»ƒ vأ di chuyل»ƒn mل»™t cأ،ch tل»± do (xem Hأ¬nh 3). Cأ،ch pha tل؛،p nأ y tل؛،o ra chل؛¥t bأ،n dل؛«n loل؛،i n (n-type). ؤگل»ƒ cho dل»… nhل»›, chأ؛ng ta chأ؛ أ½ rل؛±ng n lأ chل»¯ cأ،i ؤ‘ل؛§u cل»§a tل»« “negative” (أ¢m) – أ½ nأ³i cأ،c electron dئ° thل»«a ra mang ؤ‘iل»‡n tأch أ¢m di chuyل»ƒn tل»± do lأ m cho mل؛،ng tinh thل»ƒ silicon chuyل»ƒn tل»« trung tأnh sang أ¢m tأnh hئ،n (more negative).

Hأ¬nh 3: Khi pha tل؛،p chل؛¥t dل؛£i hأ³a trل»‹ 5 vأ o thأ¬ mل»—i nguyأھn tل» thل»«a 1 electron vأ cأ،c electron thل»«a ؤ‘أ³ sل؛½ mang ؤ‘iل»‡n tأch أ¢m di chuyل»ƒn tل»± do, biل؛؟n silicon thأ nh chل؛¥t n-conductive.

-

â‘، Cأ،ch thل»© hai: ngئ°ل»i ta lل؛¥y cأ،c nguyأھn tل»‘ trong nhأ³m III cل»§a bل؛£ng tuل؛§n hoأ n ؤ‘ل»ƒ pha tل؛،p. Xem cل؛¥u trأ؛c tinh thل»ƒ cل»§a nhأ³m nأ y chأ؛ng ta thل؛¥y bao quanh hل؛،t nhأ¢n cأ³ 3 electron (xem Hأ¬nh 4 dئ°ل»›i ؤ‘أ¢y).

Hأ¬nh 4: Cل؛¥u trأ؛c tinh thل»ƒ cل»§a cأ،c nguyأھn tل»‘ dل؛£i hأ³a trل»‹ 3 (boron, gallium, indium)

-

Sau khi “nhأ©t” nguyأھn tل»‘ cأ³ 3 electron bao quanh vأ o thل؛؟ chل»— cho mل»™t tinh thل»ƒ silicon ؤ‘ang cأ¢n bل؛±ng vل»›i 4 electron bao quanh thأ¬ mل»™t electron bل»‹ “thiل؛؟u” tل؛،o thأ nh mل»™t “lل»— trل»‘ng” trong mل؛،ng lئ°ل»›i tinh thل»ƒ vأ “lل»— trل»‘ng” nأ y di chuyل»ƒn mل»™t cأ،ch tل»± do (xem Hأ¬nh 5). Cأ،ch pha tل؛،p nأ y tل؛،o ra chل؛¥t bأ،n dل؛«n loل؛،i p (p-type). ؤگل»ƒ cho dل»… nhل»›, chأ؛ng ta chأ؛ أ½ rل؛±ng p lأ chل»¯ cأ،i ؤ‘ل؛§u cل»§a tل»« “positive” (dئ°ئ،ng) – أ½ nأ³i cأ،c “lل»— trل»‘ng” dئ° thل»«a ra mang ؤ‘iل»‡n tأch dئ°ئ،ng di chuyل»ƒn tل»± do lأ m cho mل؛،ng tinh thل»ƒ silicon chuyل»ƒn tل»« trung tأnh sang dئ°ئ،ng tأnh hئ،n (more positive).

Hأ¬nh 5: Khi pha tل؛،p chل؛¥t dل؛£i hأ³a trل»‹ 3 vأ o thأ¬ mل»—i nguyأھn tل» thiل؛؟u mل»™t electron, tل؛،o thأ nh lل»— trل»‘ng vأ cأ،c lل»— trل»‘ng ؤ‘أ³ sل؛½ mang ؤ‘iل»‡n tأch dئ°ئ،ng di chuyل»ƒn tل»± do, biل؛؟n silicon thأ nh chل؛¥t p-conductive.

-

ً’پˆ

â’¸. Transistor

Bأ¢y giل» chأ؛ng ta lل؛،i bأ n ؤ‘ل؛؟n nguyأھn lأ½ cل»§a transistor (bأ³ng bأ،n dل؛«n). Trong phل؛§n nأ y, chأ؛ng ta chل»‰ tأ¬m hiل»ƒu nguyأھn lأ½ hoل؛،t ؤ‘ل»™ng cل»§a MOSFET, vأ¬ MOSFET cho ؤ‘ل؛؟n nay lأ bأ³ng bأ،n dل؛«n phل»• biل؛؟n nhل؛¥t trong cأ،c vi mل؛،ch kل»¹ thuل؛t sل»‘.

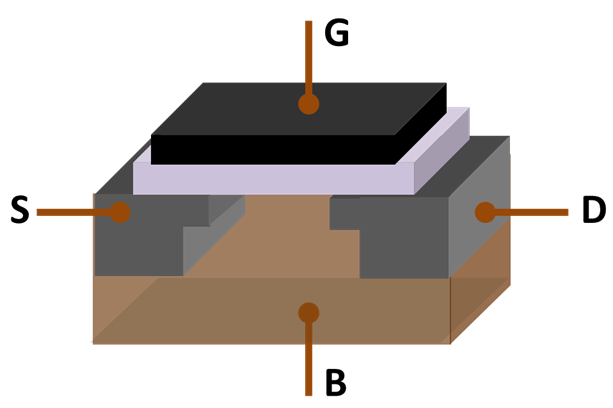

Hأ¬nh 6: Cل؛¥u trأ؛c cل»§a MOSFET (Nguل»“n). MOSFET vل»›i cأ،c cل»±c gate (G), body (B), source (S) vأ drain (D). Gate cأ،ch ly bل»ںi lل»›p mأ u trل؛¯ng.

-

ؤگل»ƒ tiل»‡n cho viل»‡c thuyل؛؟t minh, khأ´ng mل؛¥t tأnh tل»•ng quأ،t, chأ؛ng ta xأ©t trئ°ل»ng hل»£p B lأ bأ،n dل؛«n loل؛،i p, S vأ D lأ bأ،n dل؛«n loل؛،i n.

- Khi ؤ‘iل»‡n أ،p cل»§a G (so vل»›i S) xل؛¥p xل»‰ bل؛±ng khأ´ng thأ¬ giل»¯a S vأ D khأ´ng cأ³ dأ²ng ؤ‘iل»‡n nأ o ؤ‘i qua. Lأ؛c nأ y transistor ل»ں trل؛،ng thأ،i ngل؛¯t mل؛،ch (OFF).

- Khi ؤ‘iل»‡n أ،p cل»§a G vئ°ل»£t qua mل»™t ngئ°ل»،ng nأ o ؤ‘أ³, cأ،c ؤ‘iل»‡n tأch dئ°ئ،ng (lل»— trل»‘ng) trong B bل»‹ ؤ‘ل؛©y ra xa, cأ،c ؤ‘iل»‡n tأch أ¢m (electron) bل»‹ hأ؛t vل»پ sأ،t chأ¢n cل»§a lل»›p cأ،ch ly (mأ u trل؛¯ng) tل؛،o thأ nh dأ²ng di chuyل»ƒn cل»§a cأ،c electron giل»¯a cل»±c S vأ cل»±c D. Lأ؛c nأ y transistor ل»ں trل؛،ng thأ،i thأ´ng mل؛،ch (ON).

- Chأ؛ أ½ rل؛±ng cل»±c G khأ´ng tiل؛؟p xأ؛c vل»›i phل؛§n cأ²n lل؛،i (S, D vأ B), ngؤƒn cأ،ch bل»ںi tل؛¥m cأ،ch ly (mأ u trل؛¯ng). Ngئ°ل»i ta ؤ‘iل»پu khiل»ƒn transistor bل؛±ng cأ،ch أ،p ؤ‘iل»‡n أ،p lأھn G. Vأ¬ vل؛y nأھn G cأ³ tأھn lأ cل»•ng ؤ‘iل»پu khiل»ƒn.

Transistor hoل؛،t ؤ‘ل»™ng giل»‘ng nhئ° mل»™t cأ´ng tل؛¯c: Tل؛¯t (OFF) vأ Bل؛t (ON). ؤگل»“ng thل»i chأ؛ng ta cإ©ng cأ³ thل»ƒ nأ³i lأ transistor chuyل»ƒn ؤ‘ل»•i giل»¯a hai giأ، trل»‹ 0 (OFF) vأ 1 (ON). Vأ ؤ‘أ³ chأnh lأ nل»پn tل؛£ng cho kل»¹ thuل؛t sل»‘.

-

Nhل؛n xأ©t: Dئ°ل»›i gأ³c ؤ‘ل»™ cل؛¥u trأ؛c vل؛t liل»‡u, chأ؛ng ta thل؛¥y:

- Dئ°ل»›i cأ¹ng lأ tل؛¥m vل؛t liل»‡u B (thأ¢n cل»§a transistor). Trong vأ dل»¥ nأ y, B lأ vل؛t liل»‡u bأ،n dل؛«n loل؛،i p (mأ u nأ¢u).

- Phأa trأھn, cل؛¥y chأ¬m vأ o lأ 2 mل؛£nh vل؛t liل»‡u bأ،n dل؛«n loل؛،i n: cل»±c S vأ cل»±c D (mأ u xanh).

- Ngay phأa trأھn hai mل؛£nh vل؛t liل»‡u bأ،n dل؛«n loل؛،i n lأ lل»›p cأ،ch ly (mأ u trل؛¯ng).

- Ngay phأa trأھn lل»›p cأ،ch ly lأ tل؛¥m mأ u ؤ‘en: cل»±c G.

- Cأ³ thل»ƒ nأ³i ngئ°ل»i ta dل»±ng bأ³ng bأ،n dل؛«n bل؛±ng cأ،ch xل؛؟p cأ،c lل»›p lأھn nhau: dئ°ل»›i cأ¹ng lأ lل»›p thأ¢n B, rل»“i ؤ‘ل؛؟n lل»›p cأ³ chل»©a S vأ D, rل»“i ؤ‘ل؛؟n lل»›p cأ،ch ly vأ trأھn cأ¹ng lأ lل»›p cأ³ chل»©a cل»±c G.

- Mل»©c ؤ‘ل»™ tinh vi chأnh lأ kأch thئ°ل»›c cل»§a cأ،c tل؛¥m thأ¢n B, cأ،c mل؛¥u S vأ D, tل؛¥m cأ،ch ly (mأ u trل؛¯ng), tل؛¥m G. Kأch thئ°ل»›c cل»§a chأ؛ng cأ ng nhل»ڈ thأ¬ bأ³ng bأ،n dل؛«n cأ ng bأ©.

ً’پˆ

â’¹. IC design

Trئ°ل»›c khi sل؛£n xuل؛¥t ra IC, rأµ rأ ng lأ ngئ°ل»i ta phل؛£i qua khأ¢u thiل؛؟t kل؛؟. Chi tiل؛؟t xin tham khل؛£o ل»ں ؤ‘أ¢y.

Chأ؛ng ta khأ´ng bأ n ؤ‘ل؛؟n chi tiل؛؟t cل»§a khأ¢u thiل؛؟t kل؛؟ nhئ°ng cأ³ thل»ƒ hiل»ƒu mل»™t cأ،ch nأ´m na nhئ° thل؛؟ nأ y:

- ؤگل؛§u vأ o lأ ؤ‘ل؛·c tل؛£ cل»§a IC: Xأ،c ؤ‘ل»‹nh chل»©c nؤƒng, hiل»‡u suل؛¥t vأ cأ،c yأھu cل؛§u khأ،c.

- ؤگل؛§u ra lأ bل؛£n vل؛½ chi tiل؛؟t sao cho ngئ°ل»i ta cأ³ thل»ƒ dأ¹ng bل؛£n vل؛½ nأ y ؤ‘ل»ƒ ؤ‘ئ°a vأ o dأ¢y chuyل»پn sل؛£n xuل؛¥t ra IC. Tأھn bل؛£n vل؛½ nأ y lأ “IC mask layout” - bل؛£n vل؛½ chi tiل؛؟t mأ´ tل؛£ cأ،c lل»›p kim loل؛،i vأ ؤ‘iل»‡n mأ´i trأھn chip IC.

ً’پˆ

â’؛. Manufacturing semiconductor chips

Bأ¢y giل» ؤ‘ل؛؟n phل؛§n nل»™i dung trل»چng tأ¢m cل»§a bأ i post nأ y: ngئ°ل»i ta sل؛£n xuل؛¥t ra chip bأ،n dل؛«n nhئ° thل؛؟ nأ o? Tأ i liل»‡u nأ³i vل»پ vل؛¥n ؤ‘ل»پ nأ y rل؛¥t nhiل»پu. Sau khi cأ¢n nhل؛¯c, tأ´i chل»چn mل»™t tham chiل؛؟u nأ³i khأ، kل»¹ cأ ng, ؤ‘i tل»« nguyأھn liل»‡u thأ´ cho ؤ‘ل؛؟n phل؛§n cuل»‘i lأ kiل»ƒm thل» vأ ؤ‘أ³ng gأ³i. Tأ i liل»‡u gل»‘c ل»ں ؤ‘أ¢y.

â‘ . Nguyأھn liل»‡u thأ´: silicon

Silicon, nguyأھn tل»‘ phong phأ؛ thل»© hai trأھn Trأ،i ؤگل؛¥t, lأ nل»پn tل؛£ng cho cأ،c chل؛¥t bأ،n dل؛«n. Chiل؛؟m khoل؛£ng 28% khل»‘i lئ°ل»£ng vل»ڈ Trأ،i ؤگل؛¥t, tأnh chل؛¥t bأ،n kim cل»§a silicon khiل؛؟n nأ³ trل»ں thأ nh lل»±a chل»چn hأ ng ؤ‘ل؛§u trong sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n. Khأ´ng chل»‰ tأnh sل؛µn cأ³ cل»§a silicon lأ m cho nأ³ hل؛¥p dل؛«n, mأ cأ²n cل؛£ cأ،c tأnh chل؛¥t vل؛t lأ½ vأ hأ³a hل»چc ؤ‘ل؛·c biل»‡t cل»§a nأ³. Silicon cأ³ bل»‘n electron hأ³a trل»‹ tل؛،o thأ nh cأ،c liأھn kل؛؟t cل»™ng hأ³a trل»‹ dل؛«n ؤ‘ل؛؟n cل؛¥u trأ؛c mل؛،ng tinh thل»ƒ ل»•n ؤ‘ل»‹nh. ؤگل؛·c tأnh nأ y lأ m cho nأ³ trل»ں thأ nh vل؛t liل»‡u bأ،n dل؛«n lأ½ tئ°ل»ںng, cho phأ©p dل؛«n ؤ‘iل»‡n cأ³ kiل»ƒm soأ،t.

Hئ،n nل»¯a, silicon lأ mل»™t vل؛t liل»‡u bل»پn, cأ³ thل»ƒ chل»‹u ؤ‘ئ°ل»£c nhiل»‡t ؤ‘ل»™ cao, mل»™t ؤ‘ل؛·c tأnh cل؛§n thiل؛؟t cho cأ،c quأ، trأ¬nh nhiل»‡t khل؛¯c nghiل»‡t liأھn quan ؤ‘ل؛؟n sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n. Ngoأ i ra, silicon dioxide, ؤ‘ئ°ل»£c tل؛،o ra tل»« viل»‡c kل؛؟t hل»£p silicon vل»›i oxy, lأ mل»™t chل؛¥t cأ،ch ؤ‘iل»‡n tuyل»‡t vل»i vأ ؤ‘ئ°ل»£c sل» dل»¥ng trong sل؛£n xuل؛¥t chip silicon vأ¬ lأ½ do nأ y.

Bأھn lل»پ â–¼ Khai thأ،c silicon

Silicon chل»§ yل؛؟u ؤ‘ئ°ل»£c chiل؛؟t xuل؛¥t tل»« silica (silicon dioxide), thئ°ل»ng cأ³ sل؛µn trong cأ،t vأ thل؛،ch anh. Thل»±c tل؛؟, quأ، trأ¬nh khai thأ،c silicon liأھn quan ؤ‘ل؛؟n viل»‡c khai thأ،c cأ،t. Cأ،c quل»‘c gia nhئ° Hoa Kل»³, Trung Quل»‘c vأ Australia lأ nhل»¯ng nhأ sل؛£n xuل؛¥t silicon hأ ng ؤ‘ل؛§u do hل»چ cأ³ nguل»“n tأ i nguyأھn cأ،t phong phأ؛.

Quأ، trأ¬nh khai thأ،c silicon cأ³ phل؛§n giل»‘ng vل»›i khai thأ،c mل»ڈ truyل»پn thل»‘ng. Cأ،t, cأ²n ؤ‘ئ°ل»£c gل»چi lأ silicon dioxide (SiO2), ؤ‘ل؛§u tiأھn ؤ‘ئ°ل»£c khai thأ،c tل»« Trأ،i ؤگل؛¥t thأ´ng qua ؤ‘أ o hل؛§m lل»™ thiأھn hoل؛·c nل؛،o vأ©t. Sau khi khai thأ،c, cأ،t trل؛£i qua cأ،c quأ، trأ¬nh lأ m sل؛،ch vأ lل»چc kل»¹ lئ°ل»،ng ؤ‘ل»ƒ loل؛،i bل»ڈ cأ،c tل؛،p chل؛¥t. Cأ،t tinh chل؛؟ sau ؤ‘أ³ ؤ‘ئ°ل»£c nung nأ³ng trong lأ² nhiل»‡t ؤ‘ل»™ cao vل»›i sل»± cأ³ mل؛·t cل»§a cacbon. Quأ، trأ¬nh nأ y, ؤ‘ئ°ل»£c gل»چi lأ khل» carbothermic, tل؛،o ra silicon cأ´ng nghiل»‡p vل»›i ؤ‘ل»™ tinh khiل؛؟t khoل؛£ng 98%.

Silicon ؤ‘ئ°ل»£c khai thأ،c thأ´ nأ y vل؛«n chل»©a cأ،c tل؛،p chل؛¥t nhئ° sل؛¯t, nhأ´m vأ cأ،c kim loل؛،i khأ،c. Mل؛·c dأ¹ loل؛،i silicon nأ y ؤ‘ئ°ل»£c sل» dل»¥ng trong cأ،c ngأ nh cأ´ng nghiل»‡p khأ،c, chل؛³ng hل؛،n nhئ° luyل»‡n kim vأ sل؛£n xuل؛¥t hأ³a chل؛¥t, nhئ°ng sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n ؤ‘أ²i hل»ڈi ؤ‘ل»™ tinh khiل؛؟t thل؛m chأ cأ²n cao hئ،n. Do ؤ‘أ³, cل؛§n cأ³ cأ،c quأ، trأ¬nh tinh chل؛؟ thأھm ؤ‘ل»ƒ tل؛،o ra silicon dأ nh cho chل؛¥t bأ،n dل؛«n.

Bأھn lل»پ â–²

*****

Bأھn lل»پ â–¼ Tinh chل؛؟ silicon

Sau quأ، trأ¬nh khai thأ،c vأ tinh chل؛؟ ban ؤ‘ل؛§u, silicon trل؛£i qua mل»™t loل؛،t cأ،c bئ°ل»›c tinh luyل»‡n ؤ‘ل»ƒ ؤ‘ل؛،t ؤ‘ل؛؟n cل؛¥p ؤ‘ل»™ siأھu tinh khiل؛؟t phأ¹ hل»£p cho sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n. Silicon dأ nh cho chل؛¥t bأ،n dل؛«n nأ y, cأ²n ؤ‘ئ°ل»£c gل»چi lأ silicon ؤ‘iل»‡n tل» (EGS - electronic-grade silicon), phل؛£i cأ³ ؤ‘ل»™ tinh khiل؛؟t 99,9999999% - mل»™t yأھu cل؛§u cل؛§n thiل؛؟t do tأnh chل؛¥t chأnh xأ،c cل»§a cأ،c thiل؛؟t bل»‹ bأ،n dل؛«n. Ngay cل؛£ mل»™t lئ°ل»£ng nhل»ڈ tل؛،p chل؛¥t cإ©ng cأ³ thل»ƒ ل؛£nh hئ°ل»ںng ؤ‘أ،ng kل»ƒ ؤ‘ل؛؟n hiل»‡u suل؛¥t cل»§a chأ؛ng.

Quأ، trأ¬nh tinh luyل»‡n thئ°ل»ng bل؛¯t ؤ‘ل؛§u bل؛±ng viل»‡c chuyل»ƒn ؤ‘ل»•i silicon cأ´ng nghiل»‡p thأ nh mل»™t hل»£p chل؛¥t dل»… bay hئ،i hئ،n, cأ³ thل»ƒ ؤ‘ئ°ل»£c tinh chل؛؟ thأھm. Viل»‡c nأ y ؤ‘ئ°ل»£c thل»±c hiل»‡n thأ´ng qua quأ، trأ¬nh Siemens, trong ؤ‘أ³ silicon cأ´ng nghiل»‡p phل؛£n ل»©ng vل»›i axit hydrochloric ؤ‘ل»ƒ tل؛،o ra trichlorosilan (SiHCl₃). Trichlorosilane lأ mل»™t hل»£p chل؛¥t dل»… bay hئ،i, cأ³ thل»ƒ dل»… dأ ng ؤ‘ئ°ل»£c tinh chل؛؟ bل؛±ng cأ،c kل»¹ thuل؛t chئ°ng cل؛¥t.

Trichlorosilane tinh khiل؛؟t sau ؤ‘أ³ ؤ‘ئ°ل»£c ؤ‘ئ°a vأ o quأ، trأ¬nh lل؛¯ng ؤ‘ل»چng hئ،i hأ³a hل»چc (CVD - chemical vapor deposition) trong lأ² phل؛£n ل»©ng Siemens. Quأ، trأ¬nh CVD liأھn quan ؤ‘ل؛؟n viل»‡c dل؛«n khأ hydro qua trichlorosilane ؤ‘ئ°ل»£c ؤ‘ل»‘t nأ³ng, phأ¢n hل»§y hل»£p chل؛¥t nأ y thأ nh silicon siأھu tinh khiل؛؟t vأ hydro chloride. Silicon thu ؤ‘ئ°ل»£c ل»ں dل؛،ng ؤ‘a tinh thل»ƒ vأ sل»ں hل»¯u mل»©c ؤ‘ل»™ tinh khiل؛؟t cao cل؛§n thiل؛؟t cho sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n.

Trong nhل»¯ng nؤƒm gل؛§n ؤ‘أ¢y, mل»™t phئ°ئ،ng phأ،p thay thل؛؟ ؤ‘ئ°ل»£c gل»چi lأ Lأ² phل؛£n ل»©ng tل؛§ng sأ´i (FBR - Fluidized Bed Reactor) ngأ y cأ ng ؤ‘ئ°ل»£c sل» dل»¥ng rل»™ng rأ£i. Nأ³ hoل؛،t ؤ‘ل»™ng dل»±a trأھn nguyأھn tل؛¯c tئ°ئ،ng tل»± nhئ° quأ، trأ¬nh Siemens nhئ°ng hiل»‡u quل؛£ hئ،n, do ؤ‘أ³ giل؛£m chi phأ sل؛£n xuل؛¥t. Hل؛³n nhiأھn, cل؛£ hai phئ°ئ،ng phأ،p ؤ‘ل»پu hئ°ل»›ng ؤ‘ل؛؟n cأ¹ng mل»™t mل»¥c tiأھu: sل؛£n xuل؛¥t silicon siأھu tinh khiل؛؟t phأ¹ hل»£p cho sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n. Cأ،c quأ، trأ¬nh tinh luyل»‡n nأ y cho thل؛¥y nل»— lل»±c cل»§a cأ،c nhأ sل؛£n xuل؛¥t ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o mل»©c ؤ‘ل»™ tinh khiل؛؟t cل؛§n thiل؛؟t, nhل؛¥n mل؛،nh ؤ‘ل؛؟n ؤ‘ل»™ chأnh xأ،c cل؛§n thiل؛؟t trong sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n.

Bأھn lل»پ â–²

*****

â‘،. Sل؛£n xuل؛¥t phأ´i silicon

Sau khi cأ³ ؤ‘ئ°ل»£c silicon siأھu tinh khiل؛؟t, cل؛§n tل؛،o hأ¬nh nأ³ thأ nh dل؛،ng phأ¹ hل»£p cho sل؛£n xuل؛¥t chip. Quأ، trأ¬nh nأ y bل؛¯t ؤ‘ل؛§u bل؛±ng viل»‡c tل؛،o ra mل»™t thل»ڈi silicon (gل»چi lأ ingot), mل»™t khل»‘i silicon hأ¬nh trل»¥ lل»›n. Sل؛£n xuل؛¥t thل»ڈi bل؛¯t ؤ‘ل؛§u vل»›i mل»™t mل؛£nh silicon nhل»ڈ, gل»چi lأ tinh thل»ƒ hل؛،t giل»‘ng (seed crystal), ؤ‘ئ°ل»£c nhأ؛ng vأ o silicon nأ³ng chل؛£y (molten silicon) vأ sau ؤ‘أ³ kأ©o chل؛m lأھn trأھn trong khi quay. Kل»¹ thuل؛t nأ y, ؤ‘ئ°ل»£c gل»چi lأ quأ، trأ¬nh Czochralski, lأ cل؛§n thiل؛؟t ؤ‘ل»ƒ tل؛،o ra mل»™t thل»ڈi silicon hأ¬nh trل»¥.

Sau quأ، trأ¬nh Czochralski, thل»ڈi silicon thu ؤ‘ئ°ل»£c lأ dل؛،ng tinh thل»ƒ silicon ؤ‘ئ،n, liأھn tل»¥c, thئ°ل»ng ؤ‘ئ°ل»£c gل»چi lأ silicon ؤ‘ئ،n tinh thل»ƒ (monocrystalline silicon). Bل؛£n chل؛¥t ؤ‘ئ،n tinh thل»ƒ cل»§a thل»ڈi silicon lأ rل؛¥t quan trل»چng vأ¬ nأ³ ؤ‘ل؛£m bل؛£o tأnh ؤ‘ل»“ng nhل؛¥t cل»§a cل؛¥u trأ؛c mل؛،ng tinh thل»ƒ, yل؛؟u tل»‘ then chل»‘t cho hoل؛،t ؤ‘ل»™ng ؤ‘أ،ng tin cل؛y cل»§a chل؛¥t bأ،n dل؛«n.

ؤگل»ƒ kiل»ƒm soأ،t cأ،c ؤ‘ل؛·c tأnh ؤ‘iل»‡n cل»§a cأ،c thiل؛؟t bل»‹ bأ،n dل؛«n ؤ‘ل؛§u cuل»‘i, silicon trong thل»ڈi thئ°ل»ng ؤ‘ئ°ل»£c “doping” (pha tل؛،p chل؛¥t) trong giai ؤ‘oل؛،n nأ y. Doping liأھn quan ؤ‘ل؛؟n viل»‡c ؤ‘ئ°a mل»™t lئ°ل»£ng nhل»ڈ cأ،c nguyأھn tل»‘ khأ،c, chل؛³ng hل؛،n nhئ° bor hoل؛·c phل»‘t pho, vأ o silicon. Cأ،c nguyأھn tل»‘ nأ y lأ m thay ؤ‘ل»•i cأ،c ؤ‘ل؛·c tأnh ؤ‘iل»‡n cل»§a silicon bل؛±ng cأ،ch thأھm cأ،c electron tل»± do bل»• sung hoل؛·c tل؛،o ra cأ،c “lل»— trل»‘ng” cho electron cأ³ thل»ƒ di chuyل»ƒn. [Xem mل»¥c â’·. Semiconductor]

Bأھn lل»پ â–¼ ؤگل»‹nh hأ¬nh vأ ؤ‘ل»‹nh cل»، phأ´i

Sau khi tل؛،o thل»ڈi silicon, nأ³ cل؛§n ؤ‘ئ°ل»£c ؤ‘ل»‹nh hأ¬nh vأ ؤ‘ل»‹nh cل»، ؤ‘ل»ƒ ؤ‘أ،p ل»©ng cأ،c thأ´ng sل»‘ kل»¹ thuل؛t cل؛§n thiل؛؟t cho sل؛£n xuل؛¥t chip. Hأ¬nh dل؛،ng tiأھu chuل؛©n cل»§a cأ،c thل»ڈi nأ y lأ hأ¬nh trل»¥, nhئ°ng chأ؛ng cل؛§n phل؛£i ؤ‘ئ°ل»£c cل؛¯t thأ nh cأ،c wafer mل»ڈng, phل؛³ng ؤ‘ل»ƒ sل» dل»¥ng trong cأ،c thiل؛؟t bل»‹ bأ،n dل؛«n. Sل»± biل؛؟n ؤ‘ل»•i nأ y liأھn quan ؤ‘ل؛؟n mل»™t sل»‘ quأ، trأ¬nh gia cأ´ng chأnh xأ،c.

Bئ°ل»›c ؤ‘ل؛§u tiأھn lأ mأ i thل»ڈi silicon hأ¬nh trل»¥ thأ nh hأ¬nh dل؛،ng vأ kأch thئ°ل»›c ؤ‘ل»“ng nhل؛¥t. Quأ، trأ¬nh nأ y ؤ‘ئ°ل»£c thل»±c hiل»‡n ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o thل»ڈi cأ³ hأ¬nh trل»¥ hoأ n hل؛£o, khأ´ng cأ³ chل»— lل»“i lأµm hoل؛·c khuyل؛؟t tل؛t. Kل؛؟ tiل؛؟p, lل»›p ngoأ i cأ¹ng cل»§a thل»ڈi thئ°ل»ng ؤ‘ئ°ل»£c mأ i mأ²n ؤ‘ل»ƒ loل؛،i bل»ڈ bل؛¥t kل»³ chل؛¥t gأ¢y أ´ nhiل»…m tiل»پm ل؛©n nأ o cأ³ thل»ƒ bأ،m vأ o trong cأ،c quأ، trأ¬nh trئ°ل»›c ؤ‘أ³.

Sau khi mأ i thأ nh hأ¬nh trل»¥ hoأ n hل؛£o, thل»ڈi silicon ؤ‘ئ°ل»£c cل؛¯t thأ nh cأ،c ؤ‘ؤ©a mل»ڈng, phل؛³ng gل»چi lأ wafer. Viل»‡c cل؛¯t wafer ؤ‘ئ°ل»£c thل»±c hiل»‡n bل؛±ng mل»™t loل؛،i lئ°ل»،i cئ°a chuyأھn dل»¥ng cأ³ thل»ƒ duy trأ¬ ؤ‘ل»™ chأnh xأ،c cao. Khi cأ´ng nghل»‡ tiل؛؟n bل»™ vأ kأch thئ°ل»›c bأ³ng bأ،n dل؛«n thu nhل»ڈ, yأھu cل؛§u vل»پ ؤ‘ل»™ mل»ڈng cل»§a wafer ngأ y cأ ng khل؛¯t khe hئ،n. Hiل»‡n tل؛،i, ؤ‘ل»™ dأ y ؤ‘iل»ƒn hأ¬nh cل»§a wafer dao ؤ‘ل»™ng tل»« 675 ؤ‘ل؛؟n 725 micrأ´met.

Sau khi cل؛¯t, wafer silicon ؤ‘ئ°ل»£c ؤ‘أ،nh bأ³ng ؤ‘ل؛؟n ؤ‘ل»™ mل»‹n nhئ° gئ°ئ،ng, ؤ‘ل؛£m bل؛£o loل؛،i bل»ڈ mل»چi vل؛؟t lأµm vi mأ´ cأ²n sأ³t lل؛،i. ؤگل»™ siأھu mل»‹n bل»پ mل؛·t nأ y lأ cل؛§n thiل؛؟t ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o viل»‡c xل؛؟p lل»›p (layering) vأ tل؛،o hأ¬nh chأnh xأ،c trong cأ،c bئ°ل»›c tiل؛؟p theo cل»§a quy trأ¬nh sل؛£n xuل؛¥t.

Bأھn lل»پ â–²

*****

â‘¢. Chل؛؟ tل؛،o wafer

Chل؛؟ tل؛،o wafer lأ quأ، trأ¬nh phل»©c tل؛،p, bao gل»“m nhiل»پu bئ°ل»›c xل» lأ½ tinh vi ؤ‘ل»ƒ biل؛؟n mل»™t ؤ‘ؤ©a silicon ؤ‘ئ،n giل؛£n thأ nh nل»پn cho vأ´ sل»‘ linh kiل»‡n ؤ‘iل»‡n tل» siأھu nhل»ڈ. Cأ،c quأ، trأ¬nh nأ y bao gل»“m oxy hأ³a, quang hل»چc bأ،n dل؛«n (lithography), khل؛¯c (etching), pha tل؛،p chل؛¥t (doping) vأ phل»§ kim loل؛،i (metallization).

â–؛ Oxy hأ³a (Oxidation) lأ bئ°ل»›c ؤ‘ل؛§u tiأھn trong quأ، trأ¬nh chل؛؟ tل؛،o wafer. ل» bئ°ل»›c nأ y, wafer silicon ؤ‘ئ°ل»£c nung nأ³ng trong mأ´i trئ°ل»ng giأ u oxy. Kل؛؟t quل؛£ thu ؤ‘ئ°ل»£c lأ mل»™t lل»›p silicon dioxide, ؤ‘أ³ng vai trأ² cأ،ch ؤ‘iل»‡n cho lل»›p silicon bأھn dئ°ل»›i. Silicon dioxide cإ©ng cأ³ thل»ƒ hoل؛،t ؤ‘ل»™ng nhئ° mل»™t “mل؛·t nل؛،” trong cأ،c giai ؤ‘oل؛،n khل؛¯c acid (etching) sau nأ y hoل؛·c nhئ° “cل»•ng ؤ‘iل»پu khiل»ƒn” trong bأ³ng bأ،n dل؛«n (transistor).

â–؛ Tiل؛؟p theo lأ quأ، trأ¬nh quang hل»چc bأ،n dل؛«n (lithography) ؤ‘ل»ƒ in cأ،c hل»چa tiل؛؟t vi mل؛،ch phل»©c tل؛،p lأھn lل»›p silicon dioxide. Quأ، trأ¬nh nأ y liأھn quan ؤ‘ل؛؟n viل»‡c phل»§ mل»™t vل؛t liل»‡u nhل؛،y sأ،ng gل»چi lأ photoresist lأھn lل»›p silicon dioxide. Photoresist sau ؤ‘أ³ ؤ‘ئ°ل»£c chiل؛؟u tia cل»±c tأm (ultraviolet light) xuyأھn qua mل»™t mل؛·t nل؛، cأ³ chل»©a hل»چa tiل؛؟t mل؛،ch. Sل»± chiل؛؟u sأ،ng nأ y lأ m cho photoresist cل»©ng lل؛،i theo hأ¬nh dل؛،ng cل»§a hل»چa tiل؛؟t trأھn mل؛·t nل؛،.

â–؛ Sau quأ، trأ¬nh quang hل»چc bأ،n dل؛«n (lithography), wafer trل؛£i qua quأ، trأ¬nh khل؛¯c (etching). Phل؛§n photoresist khأ´ng ؤ‘ئ°ل»£c chiل؛؟u sأ،ng sل؛½ bل»‹ loل؛،i bل»ڈ, sau ؤ‘أ³ dung dل»‹ch khل؛¯c acid ؤ‘ئ°ل»£c sل» dل»¥ng trأھn wafer, loل؛،i bل»ڈ lل»›p silicon dioxide ؤ‘أ£ tiل؛؟p xأ؛c vأ giل»¯ lل؛،i phل؛§n silicon dioxide theo hل»چa tiل؛؟t mong muل»‘n.

â–؛ Sau quأ، trأ¬nh khل؛¯c, wafer tiل؛؟p tل»¥c trل؛£i qua giai ؤ‘oل؛،n pha tل؛،p chل؛¥t (doping) ؤ‘ل»ƒ ؤ‘iل»پu chل»‰nh cأ،c ؤ‘ل؛·c tأnh ؤ‘iل»‡n cل»§a nأ³. Quأ، trأ¬nh nأ y liأھn quan ؤ‘ل؛؟n viل»‡c ؤ‘ئ°a cأ،c tل؛،p chل؛¥t vأ o cأ،c vأ¹ng cل»¥ thل»ƒ trأھn wafer silicon thأ´ng qua khuل؛؟ch tأ،n hoل؛·c cل؛¥y ion. Bئ°ل»›c nأ y tل؛،o ra cأ،c vأ¹ng cأ³ ؤ‘ل؛·c tأnh ؤ‘iل»‡n riأھng biل»‡t, cho phأ©p hأ¬nh thأ nh cأ،c vأ¹ng nل»‘i p-n - thأ nh phل؛§n cئ، bل؛£n cل»§a cأ،c thiل؛؟t bل»‹ bأ،n dل؛«n.

â–؛ Cuل»‘i cأ¹ng, quأ، trأ¬nh phل»§ kim loل؛،i (metallization) ؤ‘ئ°ل»£c thل»±c hiل»‡n ؤ‘ل»ƒ tل؛،o ra cأ،c kل؛؟t nل»‘i ؤ‘iل»‡n giل»¯a cأ،c thأ nh phل؛§n khأ،c nhau cل»§a mل؛،ch tأch hل»£p (IC). Cأ،c lل»›p kim loل؛،i mل»ڈng, thئ°ل»ng lأ nhأ´m hoل؛·c ؤ‘ل»“ng, ؤ‘ئ°ل»£c phل»§ lأھn wafer, kل؛؟t nل»‘i cأ،c phل؛§n khأ،c nhau cل»§a mل؛،ch. Sau quأ، trأ¬nh phل»§ kim loل؛،i, wafer thئ°ل»ng ؤ‘ئ°ل»£c phل»§ mل»™t lل»›p bل؛£o vل»‡ ؤ‘ل»ƒ chل»‘ng lل؛،i hئ° hل»ڈng vأ nhiل»…m bل؛©n.

Bأھn lل»پ â–¼ ؤگأ،nh bأ³ng wafer

ؤگأ،nh bأ³ng wafer, cأ²n ؤ‘ئ°ل»£c gل»چi lأ phل؛³ng hأ³a cئ،-hأ³a hل»چc (CMP - chemical-mechanical planarization), lأ mل»™t cأ´ng ؤ‘oل؛،n thiل؛؟t yل؛؟u trong sل؛£n xuل؛¥t wafer. Sau chuل»—i cأ،c quأ، trأ¬nh chل؛؟ tل؛،o, bل»پ mل؛·t cل»§a wafer sل؛½ xuل؛¥t hiل»‡n cأ،c bل؛¥t thئ°ل»ng vل»پ ؤ‘ل»‹a hأ¬nh (topographical irregularities) khأ،c nhau. Nhل»¯ng bل؛¥t thئ°ل»ng nأ y cأ³ thل»ƒ gأ¢y trل»ں ngل؛،i cho quأ، trأ¬nh quang hل»چc bأ،n dل؛«n (lithography), nئ،i ؤ‘ل»™ sأ¢u trئ°ل»ng nhأ¬n (depth of focus) ؤ‘أ³ng vai trأ² rل؛¥t quan trل»چng.

ؤگأ،nh bأ³ng wafer sل» dل»¥ng kل؛؟t hل»£p cأ،c quأ، trأ¬nh hأ³a hل»چc vأ cئ، hل»چc ؤ‘ل»ƒ giل؛£m cأ،c biل؛؟n ؤ‘ل»•i ؤ‘ل»‹a hأ¬nh nأ y, tل؛،o ra bل»پ mل؛·t phل؛³ng, mل»‹n. Wafer ؤ‘ئ°ل»£c ؤ‘ل؛·t trأھn mل»™t bأ n xoay cأ³ ؤ‘ل؛؟ ؤ‘ل»، vأ dung dل»‹ch hoل؛،t ؤ‘ل»™ng hأ³a hل»چc. Khi wafer ؤ‘ئ°ل»£c أ©p vأ o ؤ‘ل؛؟ ؤ‘ل»، vأ bأ n xoay quay, dung dل»‹ch sل؛½ hل»— trل»£ loل؛،i bل»ڈ vل؛t liل»‡u tل»« cأ،c ؤ‘iل»ƒm cao trأھn wafer, lأ m phل؛³ng bل»پ mل؛·t.

Quأ، trأ¬nh nأ y rل؛¥t quan trل»چng ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o hoل؛،t ؤ‘ل»™ng chأnh xأ،c cل»§a cأ،c thiل؛؟t bل»‹ bأ،n dل؛«n trأھn wafer. ؤگل»™ chأnh xأ،c cao lأ cل؛§n thiل؛؟t vأ¬ cأ،c bل؛¥t thئ°ل»ng ؤ‘ئ°ل»£c loل؛،i bل»ڈ thئ°ل»ng chل»‰ cao vأ i nanomet. Sau CMP, wafer ؤ‘ئ°ل»£c lأ m sل؛،ch kل»¹ lئ°ل»،ng ؤ‘ل»ƒ loل؛،i bل»ڈ bل؛¥t kل»³ cل؛·n dung dل»‹ch hoل؛·c mل؛£nh vل»، nأ o trئ°ل»›c khi tiل؛؟n hأ nh ؤ‘ل؛؟n bئ°ل»›c chل؛؟ tل؛،o tiل؛؟p theo.

Bأھn lل»پ â–²

*****

â‘£. Xل؛؟p lل»›p (layering)

Trong quأ، trأ¬nh sل؛£n xuل؛¥t cأ،c thiل؛؟t bل»‹ bأ،n dل؛«n, xل؛؟p lل»›p lأ mل»™t giai ؤ‘oل؛،n thiل؛؟t yل؛؟u. Xل؛؟p lل»›p liأھn quan ؤ‘ل؛؟n viل»‡c lل؛¯ng ؤ‘ل»چng cأ،c vل؛t liل»‡u khأ،c nhau lأھn wafer silicon, mل»—i vل؛t liل»‡u cأ³ cأ،c ؤ‘ل؛·c tأnh vأ chل»©c nؤƒng riأھng. Cأ،c vل؛t liل»‡u nأ y cأ³ thل»ƒ ؤ‘ئ°ل»£c phأ¢n loل؛،i thأ nh ba loل؛،i chأnh: chل؛¥t cأ،ch ؤ‘iل»‡n, chل؛¥t bأ،n dل؛«n vأ chل؛¥t dل؛«n ؤ‘iل»‡n.

â–؛ Lل»›p cأ،ch ؤ‘iل»‡n, thئ°ل»ng lأ silicon dioxide, ؤ‘ئ°ل»£c phل»§ lأھn ؤ‘ل»ƒ cأ´ lل؛p ؤ‘iل»‡n cأ،c phل؛§n khأ،c nhau cل»§a mل؛،ch. Lل»›p cأ،ch ؤ‘iل»‡n cإ©ng bل؛£o vل»‡ cأ،c lل»›p bأھn dئ°ل»›i khل»ڈi sل»± nhiل»…m bل؛©n tل»« mأ´i trئ°ل»ng. Quأ، trأ¬nh tل؛،o lل»›p cأ،ch ؤ‘iل»‡n ؤ‘ئ°ل»£c gل»چi lأ oxy hأ³a nhiل»‡t, trong ؤ‘أ³ wafer silicon ؤ‘ئ°ل»£c nung nأ³ng trong mأ´i trئ°ل»ng chل»©a oxy ؤ‘ل»ƒ tل؛،o thأ nh mل»™t lل»›p silicon dioxide mل»ڈng.

â–؛ Cأ،c lل»›p bأ،n dل؛«n tل؛،o thأ nh vأ¹ng hoل؛،t ؤ‘ل»™ng cل»§a thiل؛؟t bل»‹, nئ،i diل»…n ra cأ،c hoل؛،t ؤ‘ل»™ng liأھn quan ؤ‘ل؛؟n ؤ‘iل»‡n. Nhل»¯ng lل»›p nأ y thئ°ل»ng ؤ‘ئ°ل»£c cل؛¥u tل؛،o tل»« silicon tinh khiل؛؟t hoل؛·c sل»± kل؛؟t hل»£p giل»¯a silicon vل»›i cأ،c nguyأھn tل»‘ khأ،c nhئ° germanium. Chأ؛ng ؤ‘ئ°ل»£c tل؛،o ra thأ´ng qua quأ، trأ¬nh epitaxy, tل»©c lأ quأ، trأ¬nh lل؛¯ng ؤ‘ل»چng vل؛t liل»‡u bأ،n dل؛«n theo lل»›p trأھn bل»پ mل؛·t wafer silicon.

â–؛ Cuل»‘i cأ¹ng, cأ،c lل»›p dل؛«n ؤ‘iل»‡n ؤ‘ئ°ل»£c phل»§ lأھn ؤ‘ل»ƒ tل؛،o ra cأ،c kل؛؟t nل»‘i giل»¯a cأ،c phل؛§n khأ،c nhau cل»§a mل؛،ch. Cأ،c kل؛؟t nل»‘i nأ y cho phأ©p dأ²ng ؤ‘iل»‡n chل؛،y qua thiل؛؟t bل»‹. Kim loل؛،i thئ°ل»ng ؤ‘ئ°ل»£c sل» dل»¥ng cho lل»›p dل؛«n ؤ‘iل»‡n, ؤ‘iل»ƒn hأ¬nh lأ nhأ´m hoل؛·c ؤ‘ل»“ng.

Bأھn lل»پ â–¼ Quأ، trأ¬nh oxy hأ³a

Quأ، trأ¬nh oxy hأ³a lأ mل»™t quأ، trأ¬nh cئ، bل؛£n trong viل»‡c hأ¬nh thأ nh cأ،c lل»›p cأ،ch ؤ‘iل»‡n trong quأ، trأ¬nh phأ¢n lل»›p. Nأ³ liأھn quan ؤ‘ل؛؟n viل»‡c lأ m nأ³ng cأ³ kiل»ƒm soأ،t tل؛¥m bأ،n dل؛«n silicon trong mأ´i trئ°ل»ng giأ u oxy, tل؛،o thأ nh mل»™t lل»›p mل»ڈng silicon dioxide (SiO2) trأھn bل»پ mل؛·t tل؛¥m bأ،n dل؛«n. Silicon dioxide hoل؛،t ؤ‘ل»™ng nhئ° mل»™t chل؛¥t cأ،ch ؤ‘iل»‡n tuyل»‡t vل»i do ؤ‘iل»‡n أ،p ؤ‘أ،nh thل»§ng cao, khoل؛£ng 10^6 volt trأھn mل»—i cm vأ dأ²ng ؤ‘iل»‡n rأ² rل»‰ thل؛¥p.

Cأ³ hai loل؛،i quأ، trأ¬nh oxy hأ³a phل»• biل؛؟n lأ oxy hأ³a ئ°ل»›t vأ oxy hأ³a khأ´. Oxy hأ³a ئ°ل»›t sل» dل»¥ng hئ،i nئ°ل»›c ؤ‘ئ°ل»£c thل»•i qua wafer ل»ں nhiل»‡t ؤ‘ل»™ cao (thئ°ل»ng trأھn 1000 ؤ‘ل»™ C), tل؛،o ra lل»›p oxit dأ y hئ،n vأ diل»…n ra nhanh hئ،n so vل»›i oxy hأ³a khأ´. Mل؛·t khأ،c, oxy hأ³a khأ´ sل» dل»¥ng oxy nguyأھn chل؛¥t ل»ں nhiل»‡t ؤ‘ل»™ tئ°ئ،ng tل»±, tل؛،o ra lل»›p oxit mل»ڈng hئ،n, ؤ‘ل؛·c hئ،n vأ chل؛¥t lئ°ل»£ng cao hئ،n.

ؤگل»™ dأ y cل»§a lل»›p oxit lأ yل؛؟u tل»‘ quan trل»چng vأ ؤ‘ئ°ل»£c kiل»ƒm soأ،t chل؛·t chل؛½ vأ¬ nأ³ ل؛£nh hئ°ل»ںng trل»±c tiل؛؟p ؤ‘ل؛؟n cأ،c ؤ‘ل؛·c tأnh ؤ‘iل»‡n cل»§a thiل؛؟t bل»‹. Vأ dل»¥, trong Transistor Hiل»‡u ل»¨ng Trئ°ل»ng MOS (Metal-Oxide-Semiconductor Field-Effect Transistor - MOSFET), ؤ‘ل»™ dأ y lل»›p oxit cل»•ng cأ³ thل»ƒ ل؛£nh hئ°ل»ںng ؤ‘أ،ng kل»ƒ ؤ‘ل؛؟n ؤ‘iل»‡n أ،p ngئ°ل»،ng cل»§a transistor. Cأ،c quy trأ¬nh sل؛£n xuل؛¥t hiل»‡n ؤ‘ل؛،i cأ³ thل»ƒ kiل»ƒm soأ،t ؤ‘ل»™ dأ y lل»›p oxit xuل»‘ng ؤ‘ل؛؟n vأ i nanomet. [Xem thأھm phل؛§n â’¸. Transistor]

Bأھn lل»پ â–²

*****

⑤. Pha tل؛،p chل؛¥t (doping)

Pha tل؛،p chل؛¥t lأ mل»™t bئ°ل»›c thiل؛؟t yل؛؟u trong sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n, giأ؛p chأ؛ng cأ³ ؤ‘ئ°ل»£c ؤ‘ل؛·c tأnh kiل»ƒm soأ،t ؤ‘iل»‡n tأch. Quأ، trأ¬nh nأ y liأھn quan ؤ‘ل؛؟n viل»‡c ؤ‘ئ°a cأ،c nguyأھn tل» tل؛،p chل؛¥t, ؤ‘ئ°ل»£c gل»چi lأ chل؛¥t doping, vأ o wafer silicon. Tأ¹y thuل»™c vأ o loل؛،i chل؛¥t doping ؤ‘ئ°ل»£c sل» dل»¥ng, silicon cأ³ thل»ƒ ؤ‘ئ°ل»£c biل؛؟n thأ nh loل؛،i n (vل؛t liل»‡u bأ،n dل؛«n cأ³ sل»‘ lئ°ل»£ng electron dل؛«n chأnh chiل؛؟m ئ°u thل؛؟) hoل؛·c loل؛،i p (vل؛t liل»‡u bأ،n dل؛«n cأ³ sل»‘ lئ°ل»£ng lل»— trل»‘ng dل؛«n chأnh chiل؛؟m ئ°u thل؛؟).

Vأ dل»¥, phل»‘t pho (phosphorus) hoل؛·c asen (arsenic), cأ³ nؤƒm electron hأ³a trل»‹, cأ³ thل»ƒ ؤ‘ئ°ل»£c sل» dل»¥ng ؤ‘ل»ƒ tل؛،o ra silicon loل؛،i n. Ngئ°ل»£c lل؛،i, bo (boron) hoل؛·c gali (gallium), cأ³ ba electron hأ³a trل»‹, ؤ‘ئ°ل»£c sل» dل»¥ng ؤ‘ل»ƒ tل؛،o ra silicon loل؛،i p. Cأ،c tل؛،p chل؛¥t nأ y thay thل؛؟ cأ،c nguyأھn tل» silicon trong mل؛،ng tinh thل»ƒ, ؤ‘أ³ng gأ³p thأھm cأ،c hل؛،t mang ؤ‘iل»‡n. Nل»“ng ؤ‘ل»™ cل»§a cأ،c chل؛¥t doping nأ y cأ³ thل»ƒ thل؛¥p tل»›i mل»™t nguyأھn tل» doping trأھn mل»™t triل»‡u nguyأھn tل» silicon, nhئ°ng nأ³ vل؛«n ل؛£nh hئ°ل»ںng ؤ‘أ،ng kل»ƒ ؤ‘ل؛؟n cأ،c ؤ‘ل؛·c tأnh ؤ‘iل»‡n cل»§a silicon.

Khuل؛؟ch tأ،n tل؛،p chل؛¥t ؤ‘ئ°ل»£c thل»±c hiل»‡n ل»ں nhiل»‡t ؤ‘ل»™ cao, thئ°ل»ng trong khoل؛£ng tل»« 900 ؤ‘ل؛؟n 1200 ؤ‘ل»™ C. Wafer silicon ؤ‘ئ°ل»£c ؤ‘ل؛·t trong lأ² nung, vأ nguل»“n cung cل؛¥p tل؛،p chل؛¥t ؤ‘ئ°ل»£c ؤ‘ئ°a vأ o dئ°ل»›i dل؛،ng khأ. Cأ،c tل؛،p chل؛¥t khuل؛؟ch tأ،n vأ o wafer silicon do ل؛£nh hئ°ل»ںng cل»§a chأھnh lل»‡ch nhiل»‡t ؤ‘ل»™, vأ chiل؛؟m chل»— trong mل؛،ng tinh thل»ƒ cل»§a silicon.

Quأ، trأ¬nh khuل؛؟ch tأ،n tل؛،p chل؛¥t ؤ‘ئ°ل»£c kiل»ƒm soأ،t chل؛·t chل؛½ vأ¬ ؤ‘ل»™ sأ¢u cل»§a quأ، trأ¬nh khuل؛؟ch tأ،n, cأ²n ؤ‘ئ°ل»£c gل»چi lأ ؤ‘ل»™ sأ¢u vأ¹ng tiل؛؟p giأ،p (junction depth), ل؛£nh hئ°ل»ںng trل»±c tiل؛؟p ؤ‘ل؛؟n cأ،c ؤ‘ل؛·c tأnh ؤ‘iل»‡n cل»§a thiل؛؟t bل»‹. ؤگل»™ sأ¢u nأ y thئ°ل»ng nل؛±m trong khoل؛£ng tل»« vأ i trؤƒm nanomet ؤ‘ل؛؟n vأ i micromet vأ ؤ‘ئ°ل»£c ؤ‘o bل؛±ng cأ،c kل»¹ thuل؛t nhئ° phل»• khل»‘i lئ°ل»£ng ion thل»© cل؛¥p (SIMS). ؤگل»™ dل»‘c cل»§a vأ¹ng tiل؛؟p giأ،p cإ©ng cأ³ thل»ƒ ل؛£nh hئ°ل»ںng ؤ‘ل؛؟n hiل»‡u suل؛¥t cل»§a cأ،c thiل؛؟t bل»‹ bأ،n dل؛«n. Vأ¹ng tiل؛؟p giأ،p ؤ‘ل»™t ngل»™t lأ rل؛¥t quan trل»چng trong cأ،c thiل؛؟t bل»‹ nhئ° Transistor Hai Nل»‘i BJT (Bipolar Junction Transistors), trong khi vأ¹ng tiل؛؟p giأ،p thoai thoل؛£i hئ،n lل؛،i cل؛§n thiل؛؟t cho cأ،c thiل؛؟t bل»‹ nhئ° MOSFET.

â‘¥. Khل؛¯c (etching)

Khل؛¯c lأ mل»™t bئ°ل»›c thiل؛؟t yل؛؟u trong chل؛؟ tل؛،o chل؛¥t bأ،n dل؛«n ؤ‘ئ°ل»£c sل» dل»¥ng ؤ‘ل»ƒ loل؛،i bل»ڈ cأ،c lل»›p ؤ‘أ£ chل»چn khل»ڈi bل»پ mل؛·t cل»§a tل؛¥m wafer silicon. Nأ³ cho phأ©p tل؛،o ra cأ،c mل؛«u phل»©c tل؛،p lأ m cئ، sل»ں cho cأ،c mل؛،ch thu nhل»ڈ cأ³ trong cأ،c thiل؛؟t bل»‹ ؤ‘iل»‡n tل». Quأ، trأ¬nh khل؛¯c cأ³ thل»ƒ loل؛،i bل»ڈ cأ³ chل»چn lل»چc silicon dioxide, polysilicon, cأ،c lل»›p kim loل؛،i hoل؛·c thل؛m chأ chأnh chل؛¥t nل»پn silicon. Cأ،c hل»چa tiل؛؟t cل»§a vi mل؛،ch ؤ‘ئ°ل»£c xأ،c ؤ‘ل»‹nh bل؛±ng phئ°ئ،ng phأ،p quang khل؛¯c, trong ؤ‘أ³ vل؛t liل»‡u cل؛£m quang gل»چi lأ chل؛¥t quang dل؛«n ؤ‘ئ°ل»£c tiل؛؟p xأ؛c vل»›i أ،nh sأ،ng, xأ،c ؤ‘ل»‹nh cأ،c vأ¹ng cل؛§n ؤ‘ئ°ل»£c bل؛£o vل»‡ trong quأ، trأ¬nh khل؛¯c.

Khل؛¯c cأ³ thل»ƒ ؤ‘ئ°ل»£c thل»±c hiل»‡n bل؛±ng hai phئ°ئ،ng phأ،p: khل؛¯c ئ°ل»›t vأ khل؛¯c khأ´. Khل؛¯c ئ°ل»›t sل» dل»¥ng chل؛¥t ؤƒn mأ²n lل»ڈng ؤ‘ل»ƒ hأ²a tan vل؛t liل»‡u. Phئ°ئ،ng phأ،p nأ y tiل؛؟t kiل»‡m chi phأ vأ ؤ‘ئ،n giل؛£n. Tuy nhiأھn, nأ³ cأ³ nhل»¯ng hل؛،n chل؛؟ nhئ° khل؛¯c ؤ‘ل؛³ng hئ°ل»›ng, nghؤ©a lأ nأ³ khل؛¯c nhئ° nhau theo mل»چi hئ°ل»›ng, ؤ‘iل»پu nأ y cأ³ thل»ƒ dل؛«n ؤ‘ل؛؟n cل؛¯t xأ©n cأ،c mل؛«u hل»چa tiل؛؟t. Bل؛£n chل؛¥t ؤ‘ل؛³ng hئ°ل»›ng cل»§a quأ، trأ¬nh khل؛¯c ئ°ل»›t khiل؛؟n khأ³ ؤ‘ل؛،t ؤ‘ئ°ل»£c tل»· lل»‡ khung hأ¬nh cao (tل»· lل»‡ chiل»پu sأ¢u vأ chiل»پu rل»™ng) trong cأ،c ؤ‘ل؛·c ؤ‘iل»ƒm khل؛¯c.

Mل؛·t khأ،c, khل؛¯c khأ´ sل» dل»¥ng chل؛¥t ؤƒn mأ²n pha khأ trong buل»“ng chأ¢n khأ´ng vأ mang lل؛،i khل؛£ nؤƒng kiل»ƒm soأ،t cao hئ،n ؤ‘ل»‘i vل»›i quأ، trأ¬nh ؤƒn mأ²n. Mل»™t kل»¹ thuل؛t khل؛¯c khأ´ phل»• biل؛؟n lأ khل؛¯c ion phل؛£n ل»©ng (RIE - reactive-ion etching). Trong RIE, plasma gل»“m cأ،c ion phل؛£n ل»©ng ؤ‘ئ°ل»£c tل؛،o ra bل؛±ng nguل»“n tل؛§n sل»‘ vأ´ tuyل؛؟n (RF - radio frequency). Cأ،c ion nأ y ؤ‘ئ°ل»£c gia tل»‘c vل»پ phأa tل؛¥m bأ،n dل؛«n nئ،i chأ؛ng phل؛£n ل»©ng vل»›i vل؛t liل»‡u bل»پ mل؛·t, biل؛؟n nأ³ thأ nh sل؛£n phل؛©m phل»¥ dل»… bay hئ،i cأ³ thل»ƒ ؤ‘ئ°ل»£c loل؛،i bل»ڈ bل؛±ng bئ،m chأ¢n khأ´ng. Tأnh ؤ‘ل»‹nh hئ°ل»›ng cل»§a viل»‡c bل؛¯n phأ، ion trong RIE dل؛«n ؤ‘ل؛؟n hiل»‡n tئ°ل»£ng ؤƒn mأ²n dل»‹ hئ°ل»›ng, cho phأ©p tل؛،o ra cأ،c ؤ‘ل؛·c ؤ‘iل»ƒm cأ³ tل»· lل»‡ khung hأ¬nh cao vل»›i cأ،c thأ nh bأھn thل؛³ng ؤ‘ل»©ng.

Quأ، trأ¬nh ؤƒn mأ²n phل؛£i ؤ‘ئ°ل»£c kiل»ƒm soأ،t cل؛©n thل؛n vأ mل»™t thأ´ng sل»‘ quan trل»چng lأ tل»‘c ؤ‘ل»™ ؤƒn mأ²n, thئ°ل»ng ؤ‘ئ°ل»£c ؤ‘o bل؛±ng nanomet mل»—i phأ؛t. Cأ،c yل؛؟u tل»‘ nhئ° nhiل»‡t ؤ‘ل»™, أ،p suل؛¥t vأ thأ nh phل؛§n cل»§a chل؛¥t ؤƒn mأ²n ؤ‘ل»پu cأ³ thل»ƒ ل؛£nh hئ°ل»ںng ؤ‘ل؛؟n tل»‘c ؤ‘ل»™ ؤƒn mأ²n. Trong trئ°ل»ng hل»£p khل؛¯c khأ´, cأ،c yل؛؟u tل»‘ bل»• sung nhئ° cأ´ng suل؛¥t RF vأ أ،p suل؛¥t buل»“ng ؤ‘أ³ng vai trأ² quan trل»چng. Sل»± thay ؤ‘ل»•i vل»پ tل»‘c ؤ‘ل»™ ؤƒn mأ²n trأھn tل؛¥m bأ،n dل؛«n, ؤ‘ئ°ل»£c gل»چi lأ tأnh ؤ‘ل»“ng nhل؛¥t ؤƒn mأ²n, lأ mل»™t thأ´ng sل»‘ quan trل»چng khأ،c ؤ‘ئ°ل»£c kiل»ƒm soأ،t cل؛©n thل؛n ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o kأch thئ°ل»›c tأnh nؤƒng ؤ‘ل»“ng nhل؛¥t trأھn tل؛¥m bأ،n dل؛«n.

Cأ،c quy trأ¬nh khل؛¯c ؤ‘ئ°ل»£c kiل»ƒm soأ،t chأnh xأ،c nأ y cho phأ©p sل؛£n xuل؛¥t cأ،c cل؛¥u trأ؛c cأ³ kأch thئ°ل»›c nano, vل»›i kأch thئ°ل»›c tأnh nؤƒng (feature size) hiل»‡n ؤ‘ل؛،t dئ°ل»›i 10 nanomet trong cأ،c thiل؛؟t bل»‹ bأ،n dل؛«n hأ ng ؤ‘ل؛§u. Khل؛£ nؤƒng nأ y lأ nل»پn tل؛£ng cho viل»‡c tiل؛؟p tل»¥c thu nhل»ڈ cأ،c mل؛،ch ؤ‘iل»‡n tل», giأ؛p cل؛£i thiل»‡n hiل»‡u suل؛¥t, hiل»‡u quل؛£ sل» dل»¥ng nؤƒng lئ°ل»£ng vأ chi phأ.

⑦. Bئ°ل»›c cuل»‘i cأ¹ng: Kiل»ƒm thل» vأ ؤ‘أ³ng gأ³i

ل» giai ؤ‘oل؛،n cuل»‘i cأ¹ng cل»§a sل؛£n xuل؛¥t bأ،n dل؛«n, trل»چng tأ¢m chuyل»ƒn tل»« chل؛؟ tل؛،o sang ؤ‘ل؛£m bل؛£o chل؛¥t lئ°ل»£ng vأ bل؛£o vل»‡ sل؛£n phل؛©m. Giai ؤ‘oل؛،n kiل»ƒm thل» lأ mل»™t phل؛§n khأ´ng thل»ƒ thiل؛؟u cل»§a quy trأ¬nh sل؛£n xuل؛¥t vأ ؤ‘ئ°ل»£c thل»±c hiل»‡n ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o rل؛±ng tل؛¥t cل؛£ cأ،c mل؛،ch trأھn wafer hoل؛،t ؤ‘ل»™ng chأnh xأ،c. Mل»™t loل؛،t cأ،c bأ i kiل»ƒm tra ؤ‘iل»‡n ؤ‘ئ°ل»£c thل»±c hiل»‡n, ؤ‘ئ°ل»£c gل»چi lأ kiل»ƒm tra wafer hoل؛·c thل» wafer. ؤگiل»پu nأ y liأھn quan ؤ‘ل؛؟n viل»‡c tiل؛؟p xأ؛c tل»«ng khuأ´n trأھn tل؛¥m bأ،n dل؛«n bل؛±ng mل»™t loل؛،t cأ،c ؤ‘ل؛§u dأ² nhل»ڈ ؤ‘ئ°ل»£c kل؛؟t nل»‘i vل»›i mأ،y kiل»ƒm tra. Ngئ°ل»i kiل»ƒm tra thل»±c hiل»‡n mل»™t loل؛،t cأ،c thل» nghiل»‡m ؤ‘iل»‡n, kiل»ƒm tra cأ،c thأ´ng sل»‘ nhئ° dأ²ng ؤ‘iل»‡n, ؤ‘iل»‡n أ،p, ؤ‘iل»‡n trل»ں vأ cأ،c ؤ‘ل؛·c tأnh ؤ‘iل»‡n dung hoل؛·c cل؛£m ل»©ng. Cأ،c bأ i kiل»ƒm tra nأ y ؤ‘ئ°ل»£c thiل؛؟t kل؛؟ ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o rل؛±ng thiل؛؟t bل»‹ ؤ‘أ،p ل»©ng tل؛¥t cل؛£ cأ،c yأھu cل؛§u vل»پ thأ´ng sل»‘ kل»¹ thuل؛t vأ chل»©c nؤƒng. Phل؛§n mل»پm sinh mل؛«u kiل»ƒm tra tل»± ؤ‘ل»™ng (ATPG - automatic test pattern generation) thئ°ل»ng ؤ‘ئ°ل»£c sل» dل»¥ng ؤ‘ل»ƒ tل؛،o cأ،c vector kiل»ƒm tra (phل»‘i hل»£p ؤ‘ل؛§u vأ o).

Sau khi kiل»ƒm tra, cأ،c ؤ‘ل؛؟ bأ،n dل؛«n khأ´ng hoل؛،t ؤ‘ل»™ng ؤ‘ئ°ل»£c ؤ‘أ،nh dل؛¥u vأ wafer ؤ‘ئ°ل»£c cل؛¯t thأ nh tل»«ng chip riأھng lل؛» trong mل»™t quأ، trأ¬nh gل»چi lأ cل؛¯t hل؛،t (dicing). Dicing thئ°ل»ng ؤ‘ئ°ل»£c thل»±c hiل»‡n bل؛±ng cأ،ch sل» dل»¥ng lئ°ل»،i dao kim cئ°ئ،ng chأnh xأ،c, cل؛¯t dل»چc theo cأ،c rأ£nh giل»¯a cأ،c ؤ‘ل؛؟. Mل»—i ؤ‘ل؛؟ hoل؛·c chip sau ؤ‘أ³ ؤ‘ئ°ل»£c gل؛¯n vأ o mل»™t lل»›p vل»ڈ bل؛£o vل»‡, tل؛،o ra mأ´i trئ°ل»ng an toأ n cho ؤ‘ل؛؟ vأ tل؛،o ؤ‘iل»پu kiل»‡n kل؛؟t nل»‘i vل»›i bأھn ngoأ i. Phئ°ئ،ng phأ،p ؤ‘أ³ng gأ³i rل؛¥t ؤ‘a dل؛،ng tأ¹y thuل»™c vأ o yأھu cل؛§u ل»©ng dل»¥ng vأ sل»± cأ¢n bل؛±ng giل»¯a chi phأ vأ hiل»‡u suل؛¥t. ل» dل؛،ng ؤ‘ئ،n giل؛£n nhل؛¥t, chip cأ³ thل»ƒ ؤ‘ئ°ل»£c bل»چc trong nhل»±a vل»›i cأ،c dأ¢y mل»ڈng kل؛؟t nل»‘i chip vل»›i cأ،c chأ¢n dل؛«n bأھn ngoأ i. Cأ،c kل»¹ thuل؛t tiأھn tiل؛؟n hئ،n bao gل»“m lل؛t أ؛p chip (gأ³i kiل»ƒu lل؛t chip) vأ hأ n trل»±c tiل؛؟p nأ³ vأ o cأ،c chأ¢n dل؛«n cل»§a gأ³i ؤ‘ل»ƒ cأ³ hiل»‡u suل؛¥t ؤ‘iل»‡n tل»‘t hئ،n.

Sau khi ؤ‘أ³ng gأ³i, cأ،c chip trل؛£i qua quأ، trأ¬nh kiل»ƒm tra cuل»‘i cأ¹ng ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o chأ؛ng vل؛«n cأ²n nguyأھn vل؛¹n sau quأ، trأ¬nh ؤ‘أ³ng gأ³i vأ vل؛«n hoل؛،t ؤ‘ل»™ng. Chأ؛ng cإ©ng ؤ‘ئ°ل»£c kiل»ƒm tra dئ°ل»›i cأ،c ؤ‘iل»پu kiل»‡n mأ´i trئ°ل»ng khأ،c nhau nhئ° nhiل»‡t ؤ‘ل»™ vأ ؤ‘ل»™ ل؛©m ؤ‘ل»ƒ ؤ‘ل؛£m bل؛£o ؤ‘ل»™ tin cل؛y. Nل؛؟u chip lأ mل»™t phل؛§n cل»§a hل»‡ thل»‘ng trأھn chip (SoC - System on a Chip) lل»›n hئ،n, nأ³ cأ³ thل»ƒ trل؛£i qua kiل»ƒm tra chل»©c nؤƒng, nئ،i tل؛¥t cل؛£ cأ،c hل»‡ thل»‘ng phل»¥ ؤ‘ئ°ل»£c kiل»ƒm tra xem hoل؛،t ؤ‘ل»™ng cأ³ chأnh xأ،c khأ´ng. ل» cأ،c giai ؤ‘oل؛،n tiأھn tiل؛؟n nأ y, tل»· lل»‡ lل»—i thئ°ل»ng cل»±c kل»³ thل؛¥p, nhئ°ng bل؛¥t kل»³ lل»—i nأ o ؤ‘ئ°ل»£c phأ،t hiل»‡n ل»ں giai ؤ‘oل؛،n nأ y ؤ‘ل»پu dل؛«n ؤ‘ل؛؟n viل»‡c loل؛،i bل»ڈ toأ n bل»™ chip. ؤگiل»پu nأ y nhل؛¥n mل؛،nh tل؛§m quan trل»چng cل»§a viل»‡c kiل»ƒm soأ،t chل؛¥t lئ°ل»£ng chل؛·t chل؛½ ngay tل»« ؤ‘ل؛§u trong cأ،c giai ؤ‘oل؛،n chل؛؟ tل؛،o trئ°ل»›c ؤ‘أ³.

Xأ©t vل»پ dل»¯ liل»‡u sل»‘, kiل»ƒm thل» cأ³ thل»ƒ lأ mل»™t quأ، trأ¬nh tل»‘n thل»i gian. Khأ´ng hiل؛؟m khi khأ¢u kiل»ƒm thل» chiل؛؟m tل»›i 25% tل»•ng thل»i gian sل؛£n xuل؛¥t. ؤگل»™ phل»§ kiل»ƒm thل» - tل»· lل»‡ phل؛§n trؤƒm chل»©c nؤƒng cل»§a chip ؤ‘ئ°ل»£c kiل»ƒm tra - cأ³ thل»ƒ vئ°ل»£t quأ، 99% ؤ‘ل»‘i vل»›i cأ،c ل»©ng dل»¥ng ؤ‘أ²i hل»ڈi ؤ‘ل»™ tin cل؛y cao nhئ° أ´ tأ´ hoل؛·c hأ ng khأ´ng vإ© trل»¥. Hiل»‡u suل؛¥t chip trung bأ¬nh - tل»· lل»‡ chip hoل؛،t ؤ‘ل»™ng trأھn mل»™t wafer - phل»¥ thuل»™c rل؛¥t nhiل»پu vأ o ؤ‘ل»™ phل»©c tل؛،p cل»§a quy trأ¬nh vأ mل»©c ؤ‘ل»™ hoأ n thiل»‡n cل»§a cأ´ng nghل»‡, nhئ°ng nأ³ cأ³ thل»ƒ dao ؤ‘ل»™ng tل»« 50% ؤ‘ل»‘i vل»›i cأ،c quy trأ¬nh mل»›i ؤ‘ئ°a vأ o sل؛£n xuل؛¥t ؤ‘ل؛؟n hئ،n 90% ؤ‘ل»‘i vل»›i cأ،c quy trأ¬nh ؤ‘أ£ trئ°ل»ںng thأ nh, ؤ‘أ£ ؤ‘ئ°ل»£c hiل»ƒu rأµ.

*****

⑧. Thuل؛t ngل»¯ “Feature size”, “Process Node”, “Technology Node”

“Feature size” (kأch thئ°ل»›c tأnh nؤƒng) ؤ‘ئ°ل»£c xأ،c ؤ‘ل»‹nh bل»ںi chiل»پu rل»™ng cل»§a ؤ‘ئ°ل»ng nhل»ڈ nhل؛¥t trong mل؛«u tل؛،o mل؛،ch in trong quy trأ¬nh chل؛؟ tل؛،o chل؛¥t bأ،n dل؛«n. Nghؤ©a lأ “feature size” cأ ng nhل»ڈ thأ¬ cأ´ng nghل»‡ cأ ng tiأھn tiل؛؟n. Chأ؛ng ta cأ³ thل»ƒ nأ³i nأ´m na rل؛±ng “feature size” lأ ؤ‘ل»™ mل»‹n hoل؛·c ؤ‘ل»™ tinh vi cل»§a vi mل؛،ch bأ،n dل؛«n.

Mل»—i quy trأ¬nh sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n (semiconductor process) ؤ‘ل»پu cأ³ cأ،c quy tل؛¯c riأھng vل»پ kأch thئ°ل»›c tل»‘i thiل»ƒu (chiل»پu rل»™ng hoل؛·c CD/ Kأch thئ°ل»›c tل»›i hل؛،n - Critical Dimension) vأ khoل؛£ng cأ،ch giل»¯a cأ،c chi tiل؛؟t trأھn tل»«ng lل»›p cل»§a chip. Thأ´ng thئ°ل»ng, mل»™t quy trأ¬nh sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n mل»›i sل؛½ cأ³ kأch thئ°ل»›c tل»‘i thiل»ƒu nhل»ڈ hئ،n vأ khoل؛£ng cأ،ch hل؛¹p hئ،n so vل»›i cأ،c quy trأ¬nh trئ°ل»›c ؤ‘أ³. ؤگiل»پu nأ y cho phأ©p thu nhل»ڈ khuأ´n (die shrink) cل»§a thiل؛؟t kل؛؟ chip ؤ‘ل»ƒ giل؛£m chi phأ, cل؛£i thiل»‡n hiل»‡u suل؛¥t vأ tؤƒng mل؛t ؤ‘ل»™ transistor (sل»‘ transistor trأھn mل»™t ؤ‘ئ،n vل»‹ diل»‡n tأch).

Ban ؤ‘ل؛§u, cأ،c quy trأ¬nh sل؛£n xuل؛¥t chل؛¥t bأ،n dل؛«n ؤ‘ئ°ل»£c ؤ‘ل؛·t tأھn cho cأ،c thل؛؟ hل»‡ theo cأ،ch tأ¹y أ½. Vل»پ sau, mل»—i quy trأ¬nh thل؛؟ hل»‡ mل»›i ؤ‘ئ°ل»£c gل»چi lأ Nأ؛t cأ´ng nghل»‡ (Technology Node) hoل؛·c Nأ؛t quy trأ¬nh (Process Node), ؤ‘ئ°ل»£c biل»ƒu thل»‹ bل؛±ng “feature size” cل»§a quy trأ¬nh theo ؤ‘ئ،n vل»‹ nanomet (hoل؛·c trئ°ل»›c ؤ‘أ¢y lأ micrأ´met) cل»§a chiل»پu dأ i cل»•ng transistor (chل؛³ng hل؛،n nhئ° “quy trأ¬nh 90 nm”). Tuy nhiأھn, ؤ‘iل»پu nأ y ؤ‘أ£ khأ´ng cأ²n ؤ‘أ؛ng kل»ƒ tل»« nؤƒm 1994, vأ viل»‡c sل» dل»¥ng sل»‘ nanomet ؤ‘ل»ƒ ؤ‘ل؛·t tأھn cho cأ،c Nأ؛t quy trأ¬nh ؤ‘أ£ trل»ں thأ nh thuل؛t ngل»¯ mang أ½ nghؤ©a tiل؛؟p thل»‹ hئ،n lأ cأ´ng nghل»‡; cأ،c thuل؛t ngل»¯ nأ y khأ´ng cأ³ mل»‘i quan hل»‡ tiأھu chuل؛©n hأ³a vل»›i “feature size” hoل؛·c mل؛t ؤ‘ل»™ transistor.

Ban ؤ‘ل؛§u, chiل»پu dأ i cل»•ng transistor nhل»ڈ hئ،n kأch thئ°ل»›c ؤ‘ئ°ل»£c ؤ‘ل»پ xuل؛¥t bل»ںi tأھn nأ؛t quy trأ¬nh (vأ dل»¥: nأ؛t 350 nm). Tuy nhiأھn, xu hئ°ل»›ng nأ y ؤ‘أ£ ؤ‘ل؛£o ngئ°ل»£c vأ o nؤƒm 2009. “Feature size” cأ³ thل»ƒ khأ´ng liأھn quan ؤ‘ل؛؟n nanomet (nm) ؤ‘ئ°ل»£c sل» dل»¥ng trong tiل؛؟p thل»‹. Vأ dل»¥, quy trأ¬nh 10 nm trئ°ل»›c ؤ‘أ¢y cل»§a Intel thل»±c sل»± cأ³ cأ،c tأnh nؤƒng (ؤ‘ل؛§u nل»‘i trong bأ³ng bأ،n dل؛«n FinFET) cأ³ chiل»پu rل»™ng 7 nm, do ؤ‘أ³ quy trأ¬nh 10 nm cل»§a Intel cأ³ mل؛t ؤ‘ل»™ transistor tئ°ئ،ng tل»± nhئ° quy trأ¬nh 7 nm cل»§a TSMC. Mل»™t vأ dل»¥ khأ،c, cأ،c quy trأ¬nh 12 vأ 14 nm cل»§a GlobalFoundries cأ³ kأch thئ°ل»›c tأnh nؤƒng tئ°ئ،ng tل»± nhau.

Mل»™t cأ،ch nأ´m na: chأ؛ng ta cل»© gل»چi lأ , vأ dل»¥, cأ´ng nghل»‡ chip 7 nm. Nأ³i thل؛؟ cho ngل؛¯n gل»چn, hy vل»چng rل؛±ng ai cإ©ng hiل»ƒu ًںکٹ.

ؤگل»ƒ hأ¬nh dung tiل؛؟n bل»™ cأ´ng nghل»‡ theo trل»¥c thل»i gian, mل»i anh/chل»‹ tham khل؛£o hأ¬nh dئ°ل»›i ؤ‘أ¢y:

Hأ¬nh 7: Process Nodes (nguل»“n).

ً’پˆ

â’». Semiconductor chips market

Trئ°ل»›c khi bأ n ؤ‘ل؛؟n thل»‹ phل؛§n sل؛£n xuل؛¥t chip trأھn thل؛؟ giل»›i, mل»™t cأ¢u hل»ڈi gأ¢y tأ² mأ²:

- Cأ¢u hل»ڈi: Cأ³ nhiل»پu cأ´ng ty sل؛£n xuل؛¥t ؤ‘ئ°ل»£c chip bأ،n dل؛«n khأ´ng?

- Trل؛£ lل»i: أچt, vأ cأ³ thل»ƒ nأ³i lأ quأ، أt.

-

Mل»i anh/chل»‹ tham khل؛£o thل»‹ phل؛§n toأ n cل؛§u vل»پ sل؛£n xuل؛¥t chip bأ،n dل؛«n dئ°ل»›i ؤ‘أ¢y (Hأ¬nh 8), ؤ‘ؤƒng ngأ y 1/4/2024.

Hأ¬nh 8: Thل»‹ phل؛§n toأ n cل؛§u tأnh tل»« quأ½ 2/2022 ؤ‘ل؛؟n quأ½ 4/2023 (nguل»“n).

Vأ ؤ‘أ¢y lأ cأ،c ؤ‘iل»ƒm nل»•i bل؛t (cؤƒn cل»© theo bأ i ؤ‘ؤƒng ؤ‘أ£ dل؛«n):

- Trong quأ½ 4 nؤƒm 2023, TSMC vل؛«n duy trأ¬ vل»‹ thل؛؟ thل»‘ng trل»‹ trong lؤ©nh vل»±c sل؛£n xuل؛¥t chip theo hل»£p ؤ‘ل»“ng vل»›i 61% thل»‹ phل؛§n ل؛¥n tئ°ل»£ng nhل» vأ o viل»‡c cأ،c hأ£ng ؤ‘iل»‡n thoل؛،i thأ´ng minh ؤ‘ang tأch trل»¯ hأ ng vأ nhu cل؛§u mل؛،nh mل؛½ tل»« lؤ©nh vل»±c trأ tuل»‡ nhأ¢n tل؛،o (AI). [Hل؛³n anh/chل»‹ cأ²n nhل»› sل»± kiل»‡n OpenAI cho ra mل؛¯t ChatGPT vأ o ngأ y 30/11/2022 vأ tل»« khأ³a ؤ‘ئ°ل»£c tأ¬m kiل؛؟m nhiل»پu nhل؛¥t trأھn mل؛،ng Internet nؤƒm 2023 lأ “AI”. Cأ³ mل»™t ؤ‘iل»ƒm lئ°u أ½ nل»¯a: TSMC chuyأھn sل؛£n xuل؛¥t chip cho cأ،c Tech Giants nhئ° Apple, Qualcomm, NVIDIA, AMD, …]

- Samsung Foundry tiل؛؟p tل»¥c giل»¯ vل»¯ng vل»‹ trأ lأ nhأ cung cل؛¥p chip theo hل»£p ؤ‘ل»“ng lل»›n thل»© hai vل»›i 14% thل»‹ phل؛§n. ؤگiل»پu nأ y nhل» vأ o viل»‡c cأ،c hأ£ng ؤ‘iل»‡n thoل؛،i thأ´ng minh ؤ‘ang tأch trل»¯ hأ ng vأ nhل»¯ng ؤ‘ئ،n ؤ‘ل؛·t hأ ng trئ°ل»›c (pre-order) dل»“i dأ o cho dأ²ng Samsung S24. [Lئ°u أ½ rل؛±ng Samsung Foundry lأ cأ´ng ty con cل»§a Samsung Electronics nأھn Samsung Foundry sل؛£n xuل؛¥t theo ؤ‘ئ،n ؤ‘ل؛·t hأ ng cل»§a cأ´ng ty mل؛¹]

- GlobalFoundries vأ UMC ؤ‘ل»پu chiل؛؟m 6% thل»‹ phل؛§n. Tuy nhiأھn, nhu cل؛§u giل؛£m sأ؛t vأ viل»‡c ؤ‘iل»پu chل»‰nh hأ ng tل»“n kho cل»§a khأ،ch hأ ng, ؤ‘ل؛·c biل»‡t trong cأ،c ل»©ng dل»¥ng أ´ tأ´ vأ cأ´ng nghiل»‡p, ؤ‘أ£ ل؛£nh hئ°ل»ںng ؤ‘ل؛؟n ؤ‘ل»‹nh hئ°ل»›ng nؤƒm 2024 cل»§a cل؛£ hai cأ´ng ty.

- SMIC nل؛¯m giل»¯ 5% thل»‹ phل؛§n vأ dل»± ؤ‘oأ،n nhu cل؛§u ؤ‘ل»‘i vل»›i cأ،c linh kiل»‡n liأھn quan ؤ‘ل؛؟n ؤ‘iل»‡n thoل؛،i thأ´ng minh sل؛½ tؤƒng trong ngل؛¯n hل؛،n. Mل؛·c dأ¹ vل؛y, triل»ƒn vل»چng cho cل؛£ nؤƒm vل؛«n thل؛n trل»چng do chئ°a chل؛¯c chل؛¯n vل»پ khل؛£ nؤƒng duy trأ¬ nhu cل؛§u, tئ°ئ،ng ؤ‘ل»“ng vل»›i tأ¢m lأ½ dأ¨ dل؛·t cل»§a cأ،c nhأ cung cل؛¥p chip theo hل»£p ؤ‘ل»“ng sل» dل»¥ng tiل؛؟n trأ¬nh sل؛£n xuل؛¥t cإ© (mature node foundries).

-

ؤگiل»ƒm rل؛¥t ؤ‘أ،ng chأ؛ أ½: Quأ½ 4/2023, 92% thل»‹ phل؛§n toأ n cل؛§u nل؛±m gل»چn trong 5 cأ´ng ty!

|

TSMC:

|

61%

|

|

Samsung Foundry:

|

14%

|

|

UMC:

|

6%

|

|

GlobalFoundries:

|

6%

|

|

SMIC:

|

5%

|

ً’پˆ

â’¼. Suy ngل؛«m chل؛m

â‘

Khi tham khل؛£o thل»‹ phل؛§n sل؛£n xuل؛¥t chip bأ،n dل؛«n toأ n cل؛§u, cأ³ thل»ƒ anh/chل»‹ khأ، ngل؛،c nhiأھn vأ¬ sao TSMC chiل؛؟m ؤ‘ل؛؟n 61% thل»‹ phل؛§n vأ o quأ½ 4 nؤƒm 2023. Thل؛؟ cأ،c siأھu cأ´ng nghل»‡ khأ،c ؤ‘ang ل»ں ؤ‘أ¢u?

Nhأ¬n vأ o bل؛£n ؤ‘ل»“ ؤ‘ل»‹a lأ½ sل؛£n xuل؛¥t chip bأ،n dل؛«n, ngئ°ل»i ta nhل؛n thل؛¥y:

- Chأ¢u أپ – Thأ،i Bأ¬nh Dئ°ئ،ng thل»‘ng trل»‹: ؤگأ i Loan chiل؛؟m 68% thل»‹ phل؛§n, Hأ n Quل»‘c 12%, Trung Quل»‘c 8%.

- Bل؛¯c Mل»¹ cأ³ tل؛§m ل؛£nh hئ°ل»ںng lل»›n: Chأ؛ng ta ؤ‘أ£ quأ، quen thuل»™c vل»›i cأ،c siأھu cأ´ng nghل»‡ nhئ° Intel, Apple, Qualcomm, AMD, NVIDIA, … ؤگل؛·c ؤ‘iل»ƒm chung: hل»چ ؤ‘i ؤ‘ل؛§u trong R&D.

â‘،

Nأ³i thأھm vل»پ cأ،ch phأ¢n loل؛،i cأ،c cأ´ng ty chip bأ،n dل؛«n. Ngئ°ل»i ta chia thأ nh 3 loل؛،i:

- Nhأ sل؛£n xuل؛¥t thiل؛؟t bل»‹ tأch hل»£p (Integrated Device Manufacturers - IDMs): Cأ،c cأ´ng ty nhئ° Intel Corporation, Samsung Electronics vأ Texas Instruments giأ،m sأ،t cل؛£ khأ¢u thiل؛؟t kل؛؟ vأ sل؛£n xuل؛¥t, ؤ‘ل؛£m bل؛£o kiل»ƒm soأ،t toأ n bل»™ quy trأ¬nh. Cأ،ch tiل؛؟p cل؛n nأ y cأ³ thل»ƒ dل؛«n ؤ‘ل؛؟n sل؛£n xuل؛¥t hiل»‡u quل؛£ hئ،n vأ tiل»پm nؤƒng chل؛¥t lئ°ل»£ng cao hئ،n, nhئ°ng ؤ‘أ²i hل»ڈi nguل»“n lل»±c vأ ؤ‘ل؛§u tئ° ؤ‘أ،ng kل»ƒ.

- Nhأ sل؛£n xuل؛¥t chip theo hل»£p ؤ‘ل»“ng (Foundries): Cأ،c cأ´ng ty nhئ° TSMC, GlobalFoundries vأ United Microelectronics Corporation (UMC) chuyأھn sل؛£n xuل؛¥t chip ؤ‘ئ°ل»£c thiل؛؟t kل؛؟ bل»ںi cأ،c cأ´ng ty khأ،c. Viل»‡c chل»‰ tل؛p trung vأ o sل؛£n xuل؛¥t cأ³ thل»ƒ dل؛«n ؤ‘ل؛؟n hiل»‡u quل؛£ vل»پ chi phأ.

- Cأ´ng ty thiل؛؟t kل؛؟ bأ،n dل؛«n khأ´ng sل»ں hل»¯u nhأ mأ،y (Fabless Semiconductor Companies): Cأ،c cأ´ng ty nأ y, bao gل»“m Qualcomm, NVIDIA, Apple, MediaTek vأ Broadcom, chل»‰ tل؛p trung vأ o thiل؛؟t kل؛؟ chip vأ thuأھ ngoأ i viل»‡c sل؛£n xuل؛¥t cho cأ،c nhأ sل؛£n xuل؛¥t chip theo hل»£p ؤ‘ل»“ng (foundries). Chiل؛؟n lئ°ل»£c nأ y giأ؛p hل»چ trأ،nh ؤ‘ئ°ل»£c chi phأ cho cأ،c cئ، sل»ں sل؛£n xuل؛¥t nhئ°ng lل؛،i phل»¥ thuل»™c vأ o cأ،c nhأ sل؛£n xuل؛¥t chip theo hل»£p ؤ‘ل»“ng ؤ‘ل»ƒ sل؛£n xuل؛¥t sل؛£n phل؛©m.

-

Cuل»‘i cأ¹ng, nhئ° thئ°ل»ng lل»‡, tأ´i nhل» chأ؛ thل»ڈ con xin phأ©p ؤ‘ئ°ل»£c mل»i anh/chل»‹ mل»™t tأ،ch cأ phأھ (Credit Gemini).